Define BUS arbitration. With a neat diagram, explain different bus arbitration mechanism

COMPUTER ORGANIZATIONExplanation

BUS ARBITRATION -

• The device that is allowed to initiate data transfers on bus at any given time is called bus-master.

• There can be only one bus master at any given time.

• Bus arbitration is the process by which next device to become the bus-master is selected and bus-mastership is transferred to it.

• There are 2 approaches to bus arbitration:

1) In centralized arbitration, a single bus-arbiter performs the required arbitration.

2) In distributed arbitration, all device participate in selection of next bus-master.

CENTRALIZED ARBITRATION -

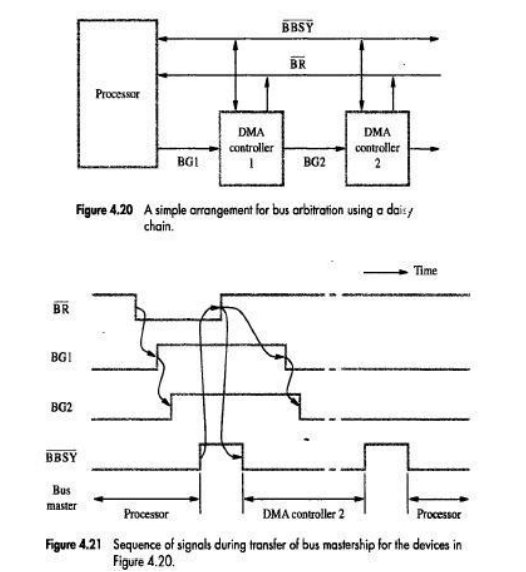

• A single bus-arbiter performs the required arbitration (Figure: 4.20 & 4.21).

• Normally, processor is the bus. master unless it grants bus mastership to one of the DMA controllers.

• A DMA controller indicates that it needs to become busmaster by activating Bus-Request line(BR).

• The signal on the BR line is the logical OR of bus-requests from all devices connected to it.

• When BR is activated, processor activates Bus-Grant signal(BG1) indicating to DMA controllers that they may use bus when it becomes free. (This signal is connected to all DMA controllers using a daisy-chain arrangement). • If DMA controller-1 is requesting the bus, it blocks propagation of grant-signal to other devices. Otherwise, it passes the grant downstream by asserting BG2.

• Current bus-master indicates to all devices that it is using bus by activating Bus-Busy line (BBSY).

• Arbiter circuit ensures that only one request is granted at any given time according to a predefined priority scheme

A conflict may arise if both the processor and a DMA controller try to use the bus at the same time to access the main memory. To resolve these conflicts, a special circuit called the bus arbiter is provided to coordinate the activities of all devices requesting memory transfers.

DISTRIBUTED ARBITRATION -

• All device participate in the selection of next bus-master (Figure 4.22)

• Each device on bus is assigned a 4-bit identification number (ID).

• When 1 or more devices request bus, they → assert Start-Arbitration signal & → place their 4-bit ID numbers on four open-collector lines ARB 0 through ARB 3 .

• A winner is selected as a result of interaction among signals transmitted over these lines by all contenders.

• Net outcome is that the code on 4 lines represents request that has the highest ID number.

• Main advantage: This approach offers higher reliability since operation of bus is not dependent on any single device.